Scaleda project overview

Scaleda (=Scalable + EDA) is an extensible FPGA EDA auxiliary tool for the IntelliJ platform. It has functions such as HDL project management, HDL language support, FPGA tool calling, etc. It is an integrated development environment for FPGA (Verilog) development, dedicated to It provides a user-friendly development platform that supports intelligent Verilog code writing and convenient simulation debugging experience. Currently, functions supported by Scaleda include:

Basic syntax functions of Verilog language (syntax highlighting, code folding, code formatting, code comments, code navigation, etc.);

Simple code completion in Verilog language;

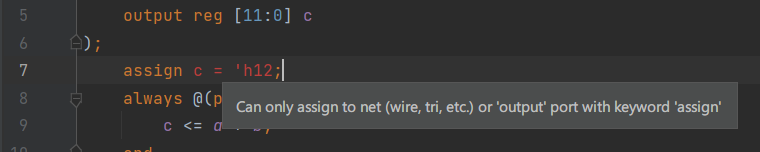

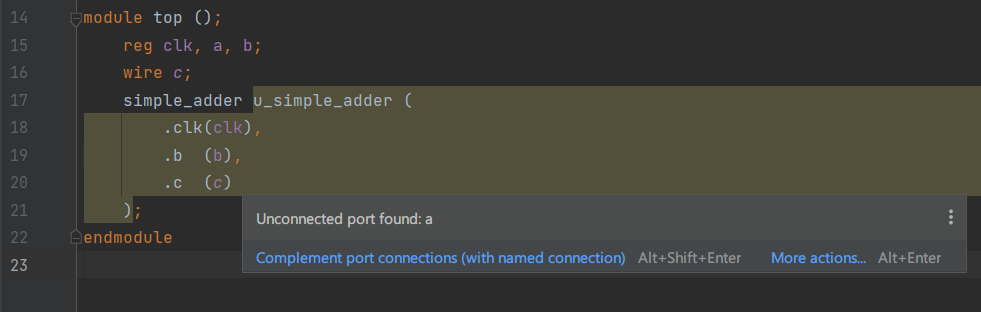

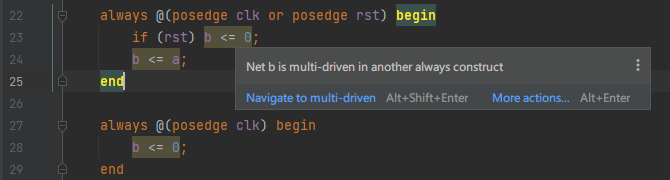

Verilog language code inspection (syntax errors and semantic errors, as well as errors such as missing ports, multiple drivers, etc.);

Verilog, SystemVerilog code formatting using Verible;

Verilog, SystemVerilog, Tcl, Bluespec SystemVerilog syntax parsing highlighting;

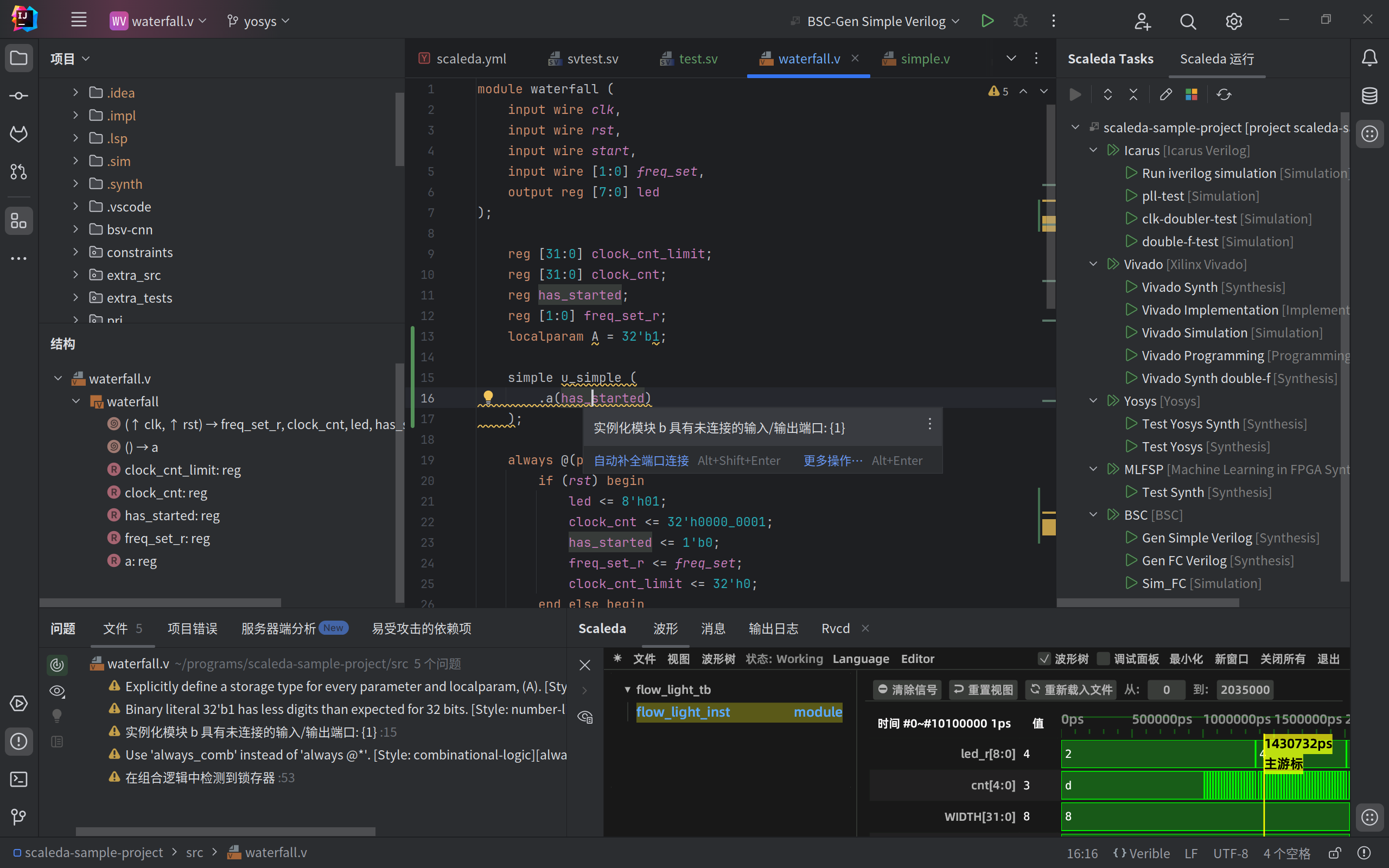

Own projects and IP structures, supporting the use of Vivado, Quartus Prime, iverilog, Yosys and other tools for simulation, synthesis, implementation and other operations;

Supports loading Vivado projects and calling synthesis, implementation and other operations;

Run server mode to perform remote EDA tasks;

Verible, Svls or custom language server (LSP) support;

International multi-display language support;

The development background of Scaleda comes from our observation of the popularity of FPGA development teaching. Traditional FPGA development revolves around EDA software provided by the manufacturer. However, such EDA software such as Vivado is often clunky and provides a poor practical development experience. Some users choose to use Visual Studio Code and develop with multiple plug-ins, but this method is usually cumbersome to configure, not friendly to beginners, and the actual experience is uneven. Based on the consideration of these issues, we hope to design a flexible and versatile FPGA development platform. Scaleda’s development vision is to provide:

Easy and intuitive configuration for an out-of-the-box experience. When users need to set software functions, a graphical interface and detailed introduction are provided.

User-friendly development experience. When users write code, they should have real-time syntax and semantic checks, and be given correction tips for common problems.

Text-based project management. Manage and generate other tool chain projects through project configuration in text format to facilitate multi-person collaboration and version control.

Rich features. In addition to basic code editing functions, it should also provide simulation, synthesis, implementation and other functions, as well as auxiliary functions such as waveform viewers.

Open source toolchain support. Take full advantage of the flexibility of the open source ecosystem and use a variety of open source tools in combination in FPGA development.

Scaleda runs on the IntelliJ platform. Although IntelliJ IDEA is an IDE designed for Java development, its powerful API extension system allows us to add support for other languages on top of it, which is similar to Visual Studio Code. Compared with Visual Studio Code, IntelliJ IDEA language supports more standardized development, is easier to implement as an “out-of-the-box” development environment, and is simpler to configure for users.

Introduction to some functions

Please click on each section title to view detailed descriptions.

Project Management

Scaleda supports creating, opening, saving and managing FPGA projects in its own format. This project system supports specifying different “tasks” (such as simulation, synthesis) for different “target platforms” (such as Xilinx Vivado, Quartus Prime) in the same project. Each task can have different configurations such as top-level modules. Parameters to achieve cross-target platform development of the same set of HDL codes. In addition, Scaleda can also directly open the Xilinx Vivado project, edit the code in it, and even call Vivado’s synthesis, implementation and other tasks.

HDL language support

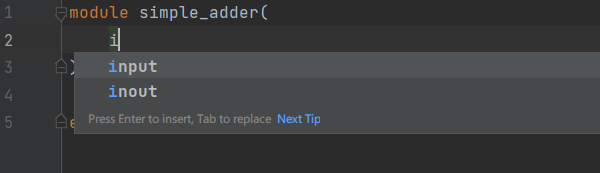

semantic level completion

Scaleda will automatically give you appropriate candidate prompts based on the context of your current code. For example:

When you are writing a module port list, keywords such as input or output will be automatically completed, and module-level parameters will also be prompted when you want to fill in the bit width.

When you are writing an expression, the list of available signals is automatically completed.

Currently, automatic completion only supports the Verilog language internally. If you need more completion functions, please use a language server that supports code completion.

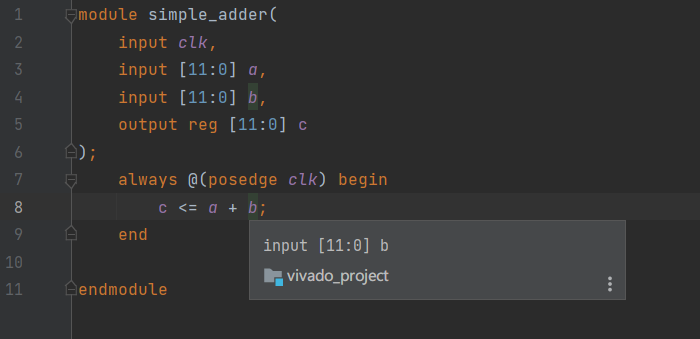

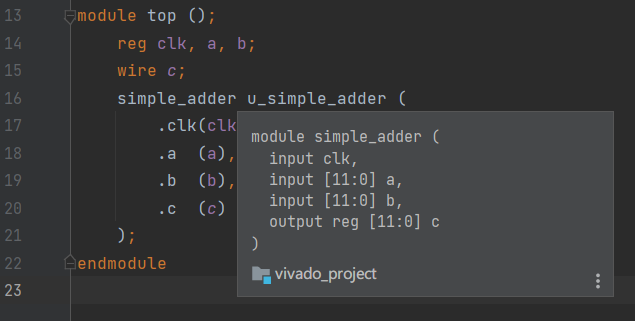

Signal type hint

All signals in the code will be represented by different fonts depending on their type. For example, all purple italic fonts represent the “line net” type, while purple regular fonts represent the “register (reg)” type. You can move the mouse over a signal, and the floating window will display the definition of the signal. You can also Ctrl-click to jump to that signal’s definition.

The same tip applies to instantiating modules. You can easily view the original module header of an instantiated module (that is, the part that defines module parameters and module ports) through the floating window, jump to the module definition, or view the properties of a certain port and parameter.

Problem code tips

Scaleda will give you possible problem tips based on your code, such as multiple drivers, unused signals, etc.

In addition to Scaleda’s built-in code inspections, code inspections provided by the language server are also displayed.

Code formatting

Currently, Scaleda’s Verilog code formatting function is implemented through Verible Formatter, which supports the formatting of Verilog and SystemVerilog codes, and Supports custom formatting options. Formatting via IDEA PSI is still under development.

IP core management

Scaleda implements IP core management functions through project configuration. Through nested project configuration files, Scaleda projects can be exported as IP cores and provide a user interface for parameter editing for quick import by other projects. At the same time, Scaleda also supports adding IP cores provided by FPGA manufacturers for users to use on specific platforms.

Tool chain call

Through Scaleda’s project configuration, tool chains such as Vivado, Quartus Prime, iverilog, and Yosys can be called for simulation, synthesis, implementation, and other operations. Scaleda has built-in preset processing for these tool chains to quickly generate projects or simulation files corresponding to the platform, and provides message parsing and error correction suggestions during the calling process.

Users who do not want to use the Scaleda project system can also directly open the Vivado project in IDEA, resolve path references, directly call the generation task, etc.

Remote service support

Scaleda supports running in server mode to perform remote EDA tasks, provides a simple JWT authentication mechanism, and supports simultaneous use by multiple users. When executing a remote task, Scaleda will submit the task to the server, and the server will call the corresponding tool chain to execute the task and return the results to the client in real time.

Command line tools

Most of Scaleda’s core features are available from the command line, such as executing tasks locally and remotely, running as a server, etc.

Wave tool

Scaleda has multiple built-in waveform viewers out of the box and provides a netlist-waveform matching jump function based on syntax parsing.

Next step

The initial goal of this project is to help beginners better understand and get started with FPGA and the world of digital logic by providing a good user experience. To achieve this goal, we have implemented some intelligent Verilog editing functions on the IntelliJ IDEA platform, and supported basic project management, tool chain calling and other functions.

In the future, we hope that Scaleda can support more tool chains, more functions, and a better user experience.

Planned features pie include:

Chisel, SpinalHDL function enhancements;

Netlist viewer;

HDL document generation;

HDL global index;

HDL code format conversion;

logic analyzer;

……

Please check Issues for planned bug fixes, feature enhancements, etc.

Scaleda is fully open source on GitHub. You are welcome to contribute code and make suggestions in Issues and feature requests, report issues.

Currently there are only two developers on Scaleda, and we hope to get more user feedback to help us better improve Scaleda. Since the developers are currently computer science students, their knowledge of digital circuit design is limited. If you wish to contribute code to Scaleda, we sincerely apologize for the mental damage caused while reading the code.