Scaleda project system introduction

The “Scaleda project” here refers to the FPGA project developed using Scaleda. A Scaleda project is an FPGA project, including one or more source files, one or more constraint files, one or more IP cores, etc. It can support a variety of tasks (such as simulation, synthesis, implementation, etc.) and can be used in multiple Execute on various platforms (such as Xilinx Vivado).

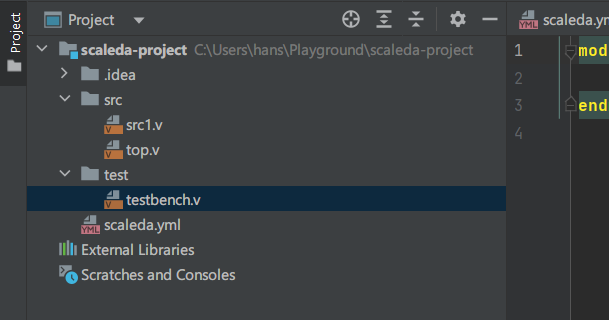

Project structure

HDL file

HDL files are the heart of the project. In a Scaleda project, HDL files are divided into two categories - source code and test files. The source code refers to the ordinary HDL module, and the test file corresponds to testbench. A project can have multiple source code files and multiple test files. By default, the source code is placed in the src folder under the project, and the test files are in the test folder.

target platform

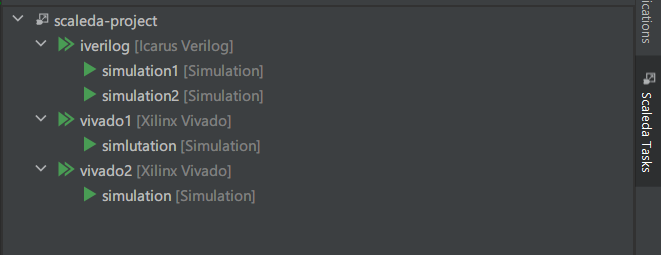

A “target” corresponds to the type of tool chain, such as Vivado or Icarus Verilog. Depending on the tool chain type, the target platform may also need to set additional parameters. For example, for the Vivado platform, the device model needs to be set. A project can have multiple target platforms, including multiple target platforms using the same tool chain.

Task

A “task” refers to an event that can be executed on a target platform. In Scaleda, there are four types of tasks:

Simulation, performing this task will use the specified testbench module to run behavioral simulation and display waveforms for debugging.

Synthesis. When executing this task, the specified top-level module will be used to perform logic synthesis and generate the EDIF netlist file corresponding to the circuit.

Implementation. To perform this task, the input EDIF netlist file will be used to implement and generate the bitstream file of the corresponding device.

Programming, performing this task will program the input bitstream file onto the FPGA hardware.

The existing tasks in the current project will be displayed in a tree structure in the Scaleda Tasks panel:

Taking the above figure as an example, there are three target platforms in this project. The target platform “iverilog” uses the Icarus Verilog tool chain, and the target platforms “vivado1” and “vivado2” use the Vivado tool chain, which may have different device models set. There are simulation, synthesis and other tasks under these target platforms, and they can set different top-level modules, test files, synthesis options, etc.

project files

The above project information is recorded in the scaleda.yml file under the project folder. The scaleda.yml file is a YAML formatted text file that can be opened with any text editor. Scaleda will automatically read the information in the scaleda.yml file to build the project system. In Scaleda, you can use the graphical interface to edit information such as tasks, target platforms, etc., without directly editing the scaleda.yml file. The scaleda.yml file can also be edited directly by the user. The following is its approximate file structure:

---

name: 项目名称

description: 项目描述

version: 项目版本

author: 项目作者,以上三项非必需

type: rtl # 项目类型,目前仅支持 rtl

source: "src/" # 源码文件夹,所有 .v 文件都会被识别为源码文件

sources:

- dir1 # 源码文件列表,与 source 可一起使用,

- dir2/file.v # 用来记录零散的源码文件

test: "test/" # 测试文件夹,所有 .v 文件都会被识别为测试文件

tests:

- dir3 # 测试文件列表,与 test 可一起使用,用来记录零散的测试文件

topModule: "top" # 项目的默认顶层模块,如果某个「目标平台」或者「任务」没有指定顶层模块,就会使用此处的默认值,可以不设置

constraintPaths:

- constraints # 约束文件目录,按照目标平台筛选约束文件

targets: # 目标平台

- name: IcarusVerilog # 目标平台标识名字

toolchain: iverilog # 工具链类型

topModule: fir_tb # 此目标平台中的顶层模块

tasks:

- name: iverilog-sim # 任务标识名字

type: simulation # 任务类型

- name: iverilog-remote

type: simulation

- name: Xilinx

toolchain: vivado

topModule: top_zynq

options: # 目标平台的选项

part: xc7z010clg400-2 # 在 Vivado 平台上选择器件型号

tasks:

- name: vivado_sim

type: simulation

topModule: fir_tb

- name: synth

type: synthesis

constraintPaths:

- constraints/vivado

- name: prog

type: programming

constraintPaths:

- constraints/vivado

- name: quartus

toolchain: quartus

topModule: flow_light_top_altera

constraintPaths:

- constraints/altera_constraints.sdc

- constraints/altera_pins.qsf

options:

part: 10AXF40AA

family: Arria 10

tasks:

- name: syn

type: synthesis

- name: prog

type: programming

In the three-level structure of project - target platform - task, topModule is inherited and covered layer by layer, while source(s), test(s), and constraintPaths are added layer by layer. When a folder is specified in these fields, all recognized files under the folder will be added to the corresponding list.